Christian Hochberger • Brent Nelson • Andreas Koch • Roger Woods • Pedro Diniz (Eds.)

# **Applied Reconfigurable Computing**

15th International Symposium, ARC 2019 Darmstadt, Germany, April 9–11, 2019 Proceedings

# Lecture Notes in Computer Science 11444

Commenced Publication in 1973

Founding and Former Series Editors:

Gerhard Goos, Juris Hartmanis, and Jan van Leeuwen

#### **Editorial Board Members**

David Hutchison

Lancaster University, Lancaster, UK

Takeo Kanade

Carnegie Mellon University, Pittsburgh, PA, USA

Josef Kittler

University of Surrey, Guildford, UK

Jon M. Kleinberg

Cornell University, Ithaca, NY, USA

Friedemann Mattern

ETH Zurich, Zurich, Switzerland

John C. Mitchell

Stanford University, Stanford, CA, USA

Moni Naor

Weizmann Institute of Science, Rehovot, Israel

C. Pandu Rangan

Indian Institute of Technology Madras, Chennai, India

Bernhard Steffen

TU Dortmund University, Dortmund, Germany

Demetri Terzopoulos

University of California, Los Angeles, CA, USA

Doug Tygar

University of California, Berkeley, CA, USA

More information about this series at http://www.springer.com/series/7407

Christian Hochberger · Brent Nelson · Andreas Koch · Roger Woods · Pedro Diniz (Eds.)

# Applied Reconfigurable Computing

15th International Symposium, ARC 2019 Darmstadt, Germany, April 9–11, 2019 Proceedings

Editors

Christian Hochberger

Technical University of Darmstadt

Darmstadt, Germany

Andreas Koch Technical University of Darmstadt Darmstadt, Germany

Pedro Diniz INESC-ID Lisbon, Portugal Brent Nelson Brigham Young University Provo, UT, USA

Roger Woods Queen's University Belfast Belfast, UK

ISSN 0302-9743 ISSN 1611-3349 (electronic) Lecture Notes in Computer Science ISBN 978-3-030-17226-8 ISBN 978-3-030-17227-5 (eBook) https://doi.org/10.1007/978-3-030-17227-5

Library of Congress Control Number: 2019936513

LNCS Sublibrary: SL1 - Theoretical Computer Science and General Issues

#### © Springer Nature Switzerland AG 2019

This work is subject to copyright. All rights are reserved by the Publisher, whether the whole or part of the material is concerned, specifically the rights of translation, reprinting, reuse of illustrations, recitation, broadcasting, reproduction on microfilms or in any other physical way, and transmission or information storage and retrieval, electronic adaptation, computer software, or by similar or dissimilar methodology now known or hereafter developed.

The use of general descriptive names, registered names, trademarks, service marks, etc. in this publication does not imply, even in the absence of a specific statement, that such names are exempt from the relevant protective laws and regulations and therefore free for general use.

The publisher, the authors and the editors are safe to assume that the advice and information in this book are believed to be true and accurate at the date of publication. Neither the publisher nor the authors or the editors give a warranty, expressed or implied, with respect to the material contained herein or for any errors or omissions that may have been made. The publisher remains neutral with regard to jurisdictional claims in published maps and institutional affiliations.

This Springer imprint is published by the registered company Springer Nature Switzerland AG The registered company address is: Gewerbestrasse 11, 6330 Cham, Switzerland

#### **Preface**

The 15th International Symposium on Applied Reconfigurable Computing (ARC) was held in April 2019 at TU Darmstadt in Germany. It is highly appropriate that ARC came to Darmstadt as TU Darmstadt was the first university worldwide to create a Chair for Electrical Engineering, awarded to Professor Erasmus Kittler in 1882.

Even closer to ARC's key focus on reconfigurable computing are two globally renowned research and high-tech institutions, both located in Darmstadt: The GSI Helmholtz Centre for Heavy Ion Research is a hotbed of high-energy physics research, employing a number of accelerators, detectors, lasers, and storage rings for advanced experiments. Discoveries made at GSI include six new elements, among them Darmstadtium (Ds, atomic number 110). Many of the scientific instruments employ reconfigurable devices such as field-programmable gate arrays (FPGAs), which are the key subject of ARC, in critical functions.

A similarly keen interest in the use of FPGAs is also prevalent in the European Space Agency (ESA), which operates its European Space Operations Centre (ESOC) in Darmstadt. FPGAs are investigated by ESA in Darmstadt both for ground as well as for space use, e.g., as components for compact CubeSats. In the course of ARC 2019, excursions to both of these fascinating institutions were part of the symposium's program.

The main program of the symposium was formed by 20 full papers and seven poster presentations. They were selected from over 50 submissions from all around the world. The selection was driven by a thorough review process with more than 200 reviews in total, which resulted in a competitive process. Besides these high-quality scientific papers, one tutorial and an invited talk complemented the program.

We hope that you find the selected papers interesting and useful for your own research or development!

February 2019

Christian Hochberger

Brent Nelson

Andreas Koch

Roger Woods

Pedro Diniz

# **Organization**

#### **General Chairs**

Andreas Koch TU Darmstadt, Germany

Roger Woods Queen's University Belfast, UK

**Program Chairs**

Christian Hochberger TU Darmstadt, Germany

Brent Nelson Brigham Young University, USA

**Proceedings Chair**

Pedro Diniz INESC-ID, Lisboa, Portugal

**Steering Committee**

Hideharu Amano Keio University, Japan

Jürgen Becker Universität Karlsruhe (TH), Germany Mladen Berekovic Universität zu Lübeck, Germany

Koen Bertels Delft University of Technology, The Netherlands

João M. P. Cardoso University of Porto, Portugal

Katherine (Compton) University of Wisconsin-Madison, USA

Morrow

George Constantinides Imperial College of Science, Technology

and Medicine, UK

Pedro Diniz INESC-ID, Lisboa, Portugal Philip H. W. Leong University of Sydney, Australia

Walid Najjar University of California Riverside, USA Roger Woods Queen's University of Belfast, UK

In memory of *Stamatis Vassiliadis* [1951–2007], ARC 2006–2007 Steering Committee member.

# **Program Committee**

Hideharu Amano Keio University, Japan

Zachary Baker Los Alamos National Laboratory, USA Juergen Becker Karlsruhe Institute of Technology, Germany

Nikolaos Bellas University of Thessaly, Greece Mladen Berekovic TU Braunschweig, Germany Joao Bispo University of Porto, Portugal Vanderlei Bonato

Christos Bouganis

João Canas Ferreira

University of São Paulo, Brazil

Imperial College London, UK

University of Porto, Portugal

University of Porto, Portugal

Luigi Carro Universidade Federal do Rio Grande do Sul, Brazil

Ray Cheung City University of Hong Kong, SAR China

Daniel Chillet CAIRN, IRISA/ENSSAT, France Steven Derrien Université de Rennes 1, France

Giorgos Dimitrakopoulos Democritus University of Thrace, Greece

Pedro Diniz INESC-ID, Lisboa, Portugal Antonio Ferrari University of Aveiro, Portugal

Ricardo Ferreira Universidade Federal de Vicosa, Brazil

Apostolos Fournaris Technological Educational Institute of Western Greece,

Greece

Roberto Giorgi University of Siena, Italy Diana Goehringer TU Dresden, Germany

Marek Gorgon AGH University of Science and Technology, Poland Frank Hannig Friedrich-Alexander University Erlangen-Nürnberg,

Germany

Jim Harkin University of Ulster, UK Christian Hochberger TU Darmstadt, Germany

Michael Huebner Brandenburg University of Technology Cottbus,

Germany

Kimon Karras Sunlight.io, Greece

Chrysovalantis Kavousianos University of Ioannina, Greece Krzysztof Kepa GE Global Research, USA

Georgios Keramidas Technological Educational Institute of Western Greece,

Greece

Andreas Koch TU Darmstadt, Germany

Tomasz Kryjak AGH University of Science and Technology, Poland

Konstantinos Masselos University of the Peloponnese, Greece

Cathal Mccabe Xilinx, Ireland

Antonio Miele Politecnico di Milano, Italy Takefumi Miyoshi e-trees.Japan, Inc., Japan

Walid Najjar University of California Riverside, USA

Brent Nelson Brigham Young University, USA

Horacio Neto Universidade de Lisboa, Portugal

Dimitris Nikolos University of Patras, Greece

Kyprianos Papadimitriou Neapolis University Pafos and Technical University

of Crete, Greece

Monica Pereira Universidade Federal do Rio Grande do Norte, Brazil Thilo Pionteck Otto-von-Guericke Universität Magdeburg, Germany

Marco Platzner University of Paderborn, Germany Mihalis Psarakis University of Piraeus, Greece

Kyle Rupnow Inspirit IoT, USA Kentaro Sano RIKEN R-CCS, Japan Marco Domenico Politecnico di Milano, Italy

Santambrogio

Yukinori Sato Toyohashi University of Technology, Japan

Antonio Carlos Schneider Universidade Federal do Rio Grande do Sul, Brazil

Beck

Yuichiro Shibata Nagasaki University, Japan

Dimitrios Soudris National Technical University of Athens, Greece

Theocharis Theocharides

George Theodoridis

David Thomas

University of Cyprus, Cyprus

University of Patras, Greece

Imperial College, London, UK

Nikolaos Voros Technological Educational Institute of Western Greece,

Greece

Chao Wang

University of Science and Technology of China, China

Markus Weinhardt

Osnabrück University of Applied Sciences, Germany

Roger Woods Queen's University Belfast, UK Yoshiki Yamaguchi University of Tsukuba, Japan

#### **Sponsors**

The 2019 Applied Reconfigurable Computing Symposium (ARC 2019) was sponsored by:

# **Contents**

| A |   | 1  | ٠, |   | 4: |    |    |

|---|---|----|----|---|----|----|----|

| A | μ | וע | Ц  | a | u  | U. | ns |

| Fault-Tolerant Architecture for On-board Dual-Core Synthetic-Aperture                                                              |     |

|------------------------------------------------------------------------------------------------------------------------------------|-----|

| Radar Imaging                                                                                                                      | 3   |

| Optimizing CNN-Based Hyperspectral Image Classification on FPGAs Shuanglong Liu, Ringo S. W. Chu, Xiwei Wang, and Wayne Luk        | 17  |

| Supporting Columnar In-memory Formats on FPGA: The Hardware Design of Fletcher for Apache Arrow                                    | 32  |

| A Novel Encoder for TDCs                                                                                                           | 48  |

| A Resource Reduced Application-Specific FPGA Switch                                                                                | 58  |

| Software-Defined FPGA Accelerator Design for Mobile Deep Learning Applications                                                     | 68  |

| Partial Reconfiguration and Security                                                                                               |     |

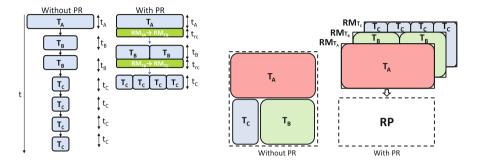

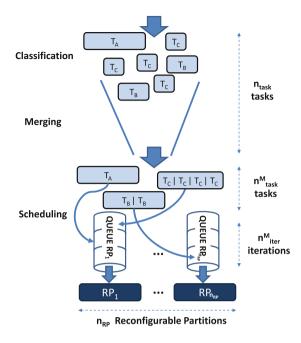

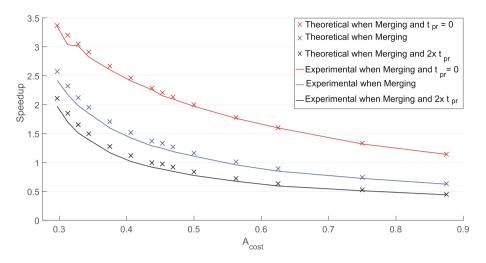

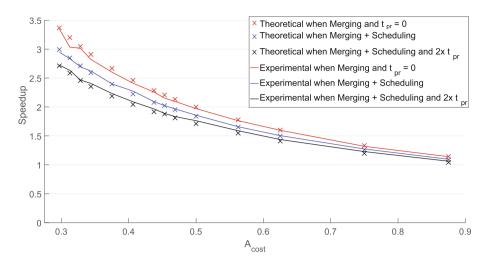

| Probabilistic Performance Modelling when Using Partial Reconfiguration to Accelerate Streaming Applications with Non-deterministic |     |

| Task Scheduling                                                                                                                    | 81  |

| Leveraging the Partial Reconfiguration Capability of FPGAs for Processor-Based Fail-Operational Systems                            | 96  |

| (ReCo)Fuse Your PRC or Lose Security: Finally Reliable Reconfiguration-Based Countermeasures on FPGAs                              | 112 |

| Kenneth Schmitz, Buse Ustaoglu, Daniel Große, and Rolf Drechsler                                                                   |     |

| Proof-Carrying Hardware Versus the Stealthy Malicious LUT                                                                                                                          | 105 |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| Hardware Trojan                                                                                                                                                                    | 127 |

| Secure Local Configuration of Intellectual Property Without a Trusted                                                                                                              |     |

| Third Party                                                                                                                                                                        | 137 |

| Image/Video Processing                                                                                                                                                             |     |

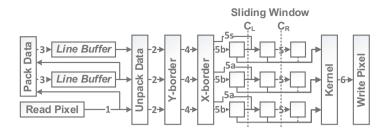

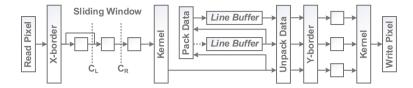

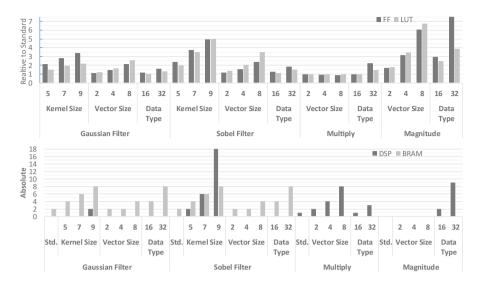

| HiFlipVX: An Open Source High-Level Synthesis FPGA Library                                                                                                                         |     |

| for Image Processing                                                                                                                                                               | 149 |

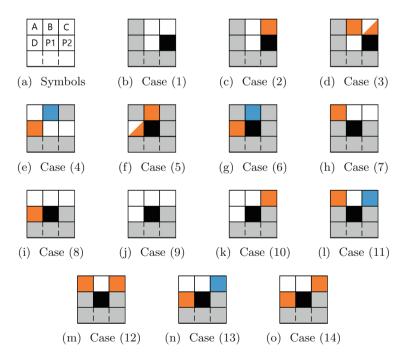

| Real-Time FPGA Implementation of Connected Component Labelling                                                                                                                     |     |

| for a 4K Video Stream                                                                                                                                                              | 165 |

| A Scalable FPGA-Based Architecture for Depth Estimation in SLAM Konstantinos Boikos and Christos-Savvas Bouganis                                                                   | 181 |

| High-Level Synthesis                                                                                                                                                               |     |

| Evaluating LULESH Kernels on OpenCL FPGA                                                                                                                                           | 199 |

| The TaPaSCo Open-Source Toolflow for the Automated Composition of Task-Based Parallel Reconfigurable Computing Systems Jens Korinth, Jaco Hofmann, Carsten Heinz, and Andreas Koch | 214 |

| Graph-Based Code Restructuring Targeting HLS for FPGAs                                                                                                                             | 230 |

| CGRAs and Vector Processing                                                                                                                                                        |     |

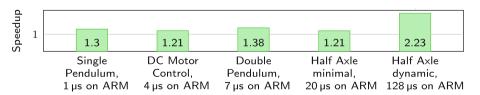

| UltraSynth: Integration of a CGRA into a Control                                                                                                                                   |     |

| Engineering Environment                                                                                                                                                            | 247 |

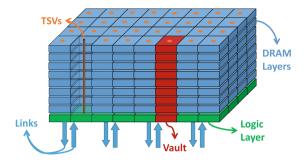

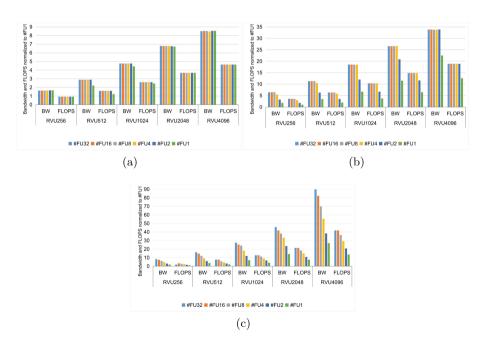

| Exploiting Reconfigurable Vector Processing for Energy-Efficient                                                                                                                   |     |

| Computation in 3D-Stacked Memories                                                                                                                                                 | 262 |

| Contents | xiii |

|----------|------|

| Contents | AIII |

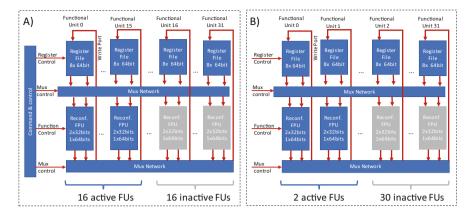

| Automatic Toolflow for VCGRA Generation to Enable CGRA Evaluation for Arithmetic Algorithms                                   | 277 |

|-------------------------------------------------------------------------------------------------------------------------------|-----|

| Architectures                                                                                                                 |     |

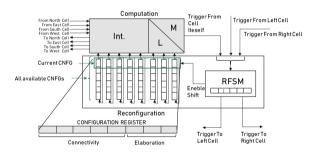

| ReM: A Reconfigurable Multipotent Cell for New Distributed Reconfigurable Architectures                                       | 295 |

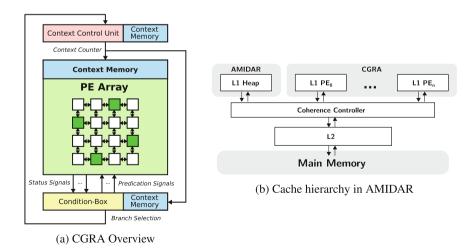

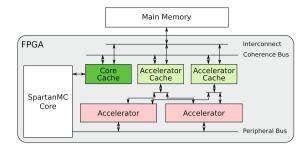

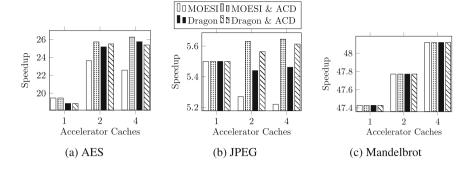

| Update or Invalidate: Influence of Coherence Protocols on Configurable HW Accelerators                                        | 305 |

| Design Frameworks and Methodology                                                                                             |     |

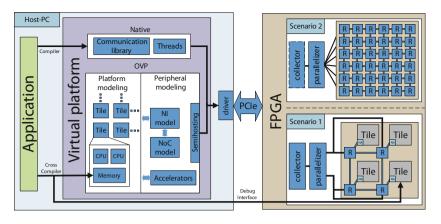

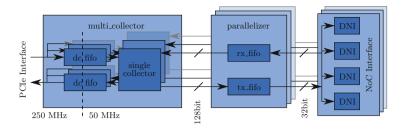

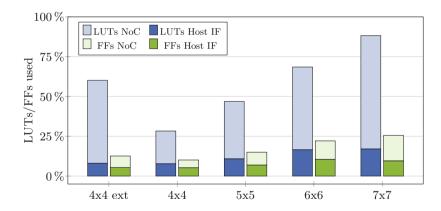

| Hybrid Prototyping for Manycore Design and Validation                                                                         | 319 |

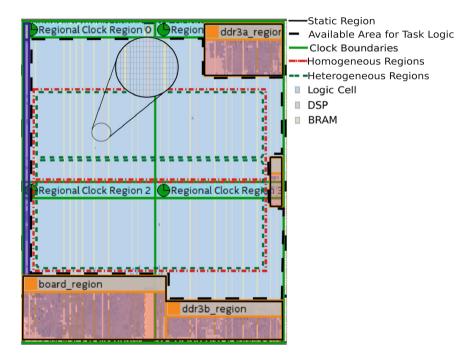

| Evaluation of FPGA Partitioning Schemes for Time and Space Sharing of Heterogeneous Tasks                                     | 334 |

| Invited Talk                                                                                                                  |     |

| Third Party CAD Tools for FPGA Design—A Survey of the Current Landscape                                                       | 353 |

| Convolutional Neural Networks                                                                                                 |     |

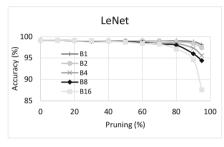

| Filter-Wise Pruning Approach to FPGA Implementation of Fully Convolutional Network for Semantic Segmentation                  | 371 |

| Exploring Data Size to Run Convolutional Neural Networks in Low Density FPGAs.  Ana Gonçalves, Tiago Peres, and Mário Véstias | 387 |

| Faster Convolutional Neural Networks in Low Density FPGAs Using Block Pruning                                                 | 402 |

| Author Index                                                                                                                  | 417 |

# Fault-Tolerant Architecture for On-board Dual-Core Synthetic-Aperture Radar Imaging

Helena Cruz<sup>1,2</sup>, Rui Policarpo Duarte<sup>1,2</sup>, and Horácio Neto<sup>1,2</sup>, and Horácio Neto<sup>1,2</sup>

<sup>1</sup> INESC-ID, Rua Alves Redol, 9, Lisbon, Portugal

<sup>2</sup> Instituto Superior Técnico, University of Lisbon, Lisbon, Portugal {helena.cruz,rui.duarte,horacio.neto}@tecnico.ulisboa.pt

Abstract. In this research work, an on-board dual-core embedded architecture was developed for SAR imaging systems, implementing a reduced-precision redundancy fault-tolerance mechanism. This architecture protects the execution of the BackProjection Algorithm, capable of generating acceptable SAR images in embedded systems subjected to errors from the space environment. The proposed solution was implemented on a Xilinx SoC device with a dual-core processor. The present work was able to produced images with less 0.65 dB on average, than the fault-free image, at the expense of a time overhead up to 33%, when in the presence of error rates similar to the ones measured in space environment. Notwithstanding, the BackProjection algorithm executed up to 1.58 times faster than its single-core version without any fault-tolerance mechanisms.

**Keywords:** Synthetic-Aperture Radar  $\cdot$  BackProjection Algorithm  $\cdot$  Approximate computing  $\cdot$  FPGA  $\cdot$  Dual-core  $\cdot$  SoC

#### 1 Introduction

There is an increasing need for satellites, drones and Unmanned Aerial Vehicles (UAVs) to have lightweight, small, autonomous, portable, battery-powered systems able to generate Synthetic-Aperture Radar (SAR) images on-board and broadcasting them to Earth, avoiding the time-consuming data processing at the receivers.

SAR is a form of radar used to generate 2D and 3D images of Earth which is usually mounted on moving platforms such as satellites, aircrafts and drones.

This work was supported by national funds through Fundação para a Ciencia e a Tecnologia (FCT) with reference UID/CEC/50021/2019, and project SARRROCA, "Synthetic Aperture Radar Robust Reconfigurable Optimized Computing Architecture" with reference: PTDC/EEI-HAC/31819/2017, funded by FCT/MCTES through national funds, and POCI - Programa Operacional Competitividade e Internacionalização e PORLisboa - Programa Operacional Regional de Lisboa.

<sup>©</sup> Springer Nature Switzerland AG 2019 C. Hochberger et al. (Eds.): ARC 2019, LNCS 11444, pp. 3–16, 2019. https://doi.org/10.1007/978-3-030-17227-5\_1

SAR can operate through clouds, smoke and rain and does not require a light source, making it a very attractive method to monitor the Earth, in particular, the melting of polar ice-caps, sea level rise, wind patterns, erosion, drought prediction, precipitation, landslide areas, oil spills, deforestation, fires, natural disasters such as hurricanes, volcano eruptions and earthquakes.

Space is a harsh environment for electronic circuits and systems as it can cause temporary or permanent errors on them. Therefore, systems designed for spacecrafts or satellites must be reliable and tolerate space radiation. The main radiation sources in space are: high-energy cosmic ray protons and heavy ions, protons and heavy ions from solar flares, heavy ions trapped in the magnetosphere and protons and electrons trapped in the Van Allen belts [3,15,20]. These radiation sources are capable of deteriorating the electronic systems and provoking bit-flips, leading to failures in electronic systems [2,11,14,16]. Fault tolerance mechanisms are used to increase the reliability of these systems at the expense of extra mechanisms, processing time and power.

BackProjection is an algorithm for SAR image generation that is capable of generating high quality images. BackProjection is considered the reference algorithm for image formation since it does not introduce any assumptions or approximations regarding the image. However, it is a very computationally intensive algorithm. Therefore, typical fault-tolerance mechanisms will introduce a huge penalty on its performance.

System-on-Chip (SoC) Field-Programmable Gate Arrays (FPGAs) were chosen as a target device because of their power efficiency, performance and reconfigurability, which are very important characteristics for space systems. Furthermore, the use of a SoC FPGA will enable future developments of dedicated hardware accelerators to improve the performance of the system.

# 2 Background

#### 2.1 Synthetic-Aperture Radar

SAR is a form of radar used to generate 2D and 3D high resolution images of objects. Unlike other radars, SAR uses the relative motion between the radar and the target to obtain its high resolution. This motion is achieved by mounting the radar on moving platforms such as satellites, aircrafts or drones, as illustrated in Fig. 1. The distance between the radar and the target in the time between the transmission and reception of pulses creates the synthetic antenna aperture. The larger the aperture, the higher the resolution of the image, regardless of the type of aperture used. To generate SAR images, it is necessary to use an image generation algorithm, such as the BackProjection Algorithm, described below.

#### 2.2 BackProjection Algorithm

The BackProjection algorithm takes the following values as input: number of pulses, location of the platform for each pulse, the carrier wave number, the radial

Fig. 1. Example of geometries involved in a SAR system.

distance between the plane and target, the range bin resolution, the real distance between two pixels and the measured heights. The BackProjection algorithm, from [1], performs the following steps for each pixel and each pulse:

- 1. Computes the distance from the platform to the pixel.

- 2. Converts the distance to an associated position (range) in the data set (received echoes).

- 3. Samples at the computed range using linear interpolation, using Eq. 1 [13].

$$g_{x,y}(r_k) = g(n) + \frac{g(n+1) - g(n)}{r(n+1) - r(n)} \cdot (r_k - r(n))$$

(1)

4. Scales the sampled value by a matched filter to form the pixel contribution. This value is calculated using Eq. 2, and dr is calculated using Eq. 3, as in [13].

$$e^{i\omega 2|\overrightarrow{r_k}|} = \cos(2 \cdot \omega \cdot dr) + i\sin(2 \cdot \omega \cdot dr)$$

(2)

$$dr = \sqrt{(x - x_k)^2 + (y - y_k)^2 + (z - z_k)^2} - r_c$$

(3)

5. Accumulates the contribution into the pixel. The final value of each pixel is given by Eq. 4 [13].

$$f(x,y) = \sum_{k} g_{x,y}(r_k, \theta_k) \cdot e^{i \cdot \omega \cdot 2|\overrightarrow{r_k}|}$$

(4)

Table 1 summarizes the algorithm's variables and their meaning.

| Variable                 | Meaning                                                               |

|--------------------------|-----------------------------------------------------------------------|

| g(n)                     | Wave sample in the previous adjacent range bin                        |

| g(n+1)                   | Wave sample in the following adjacent range bin                       |

| r(n)                     | Corresponding range to the previous adjacent bin                      |

| r(n+1)                   | Corresponding range to the following adjacent bin                     |

| $r_k$                    | Range from pixel $f(x,y)$ to aperture point $\theta_k$                |

| dr                       | Differential range from platform to each pixel versus center of swath |

| $x_k, y_k, z_k$          | Radar platform location in Cartesian coordinates                      |

| x, y, z                  | Pixel location in Cartesian coordinates                               |

| $r_c$                    | Range to center of the swath from radar platform                      |

| f(x,y)                   | Value of each pixel $(x, y)$                                          |

| $\theta_k$               | Aperture point                                                        |

| $r_k$                    | Range from pixel $f(x,y)$ to aperture point $\theta_k$                |

| ω                        | Minimal angular velocity of wave                                      |

| $g_{x,y}(r_k, \theta_k)$ | Wave reflection received at $r_k$ at $\theta_k$                       |

Table 1. Variables and their meaning

**Algorithm 1.1.** BackProjection algorithm pseudocode. **Source:** PERFECT Manual Suite [1].

```

1: for all pixels k do

2:

f_k \leftarrow 0

3:

for all pulses p do

4:

R \leftarrow ||a_k - v_p||

b \leftarrow \lfloor (R - R0)/\Delta R \rfloor

5:

6:

if b \in [0, N_b p - 2] then

7:

w \leftarrow |(R - R0)/\Delta R| - b

8:

s \leftarrow (1 - w) \cdot g(p, b) + w \cdot g(p, b + 1)

f_k \leftarrow f_k + e^{i \cdot k_u \cdot R}

9:

end if

10:

end for

11:

12: end for

```

The pseudocode to compute the aforementioned steps is shown in Algorithm 1.1.  $k_u$  represents the wave number and is given by  $\frac{2\pi f_c}{c}$ , where  $f_c$  is the carrier frequency of the waveform and c is the speed of light,  $a_k$  refers to the position of the pixel, and  $v_p$ , corresponds to the platform position.

The BackProjection algorithm implementation used in this study was taken from the PERFECT Suite [1] and is written in C. This suite also contains three input image sets: small, medium and large, which produce images of sizes  $512 \times 512$ ,  $1024 \times 1024$  and  $2048 \times 2048$  pixels, respectively.

#### 2.3 SAR Image Quality Assessment

The metric used to evaluate the quality of a SAR image is the Signal-To-Noise Ratio (SNR). The SNR measures the difference between the desired signal and the background noise, see Eq. 5. The larger the SNR value, the greater the agreement between the pixel values. Values above 100 dB are considered reasonable [1].

$$SNR_{dB} = 10\log_{10}\left(\frac{\sum_{k=1}^{N} |r_k|^2}{\sum_{k=1}^{N} |r_k - t_k|^2}\right)$$

(5)

- $r_k$  Reference value for k-th pixel.

- $t_k$  Test value for k-th pixel.

- N Number of pixel to compare.

#### 2.4 Fault-Tolerant SAR Image Generation

Precise fault-tolerant mechanisms consist of repetitions of the same operations in one or more units and evaluate which is the most voted result, regarding it as the correct one. The most common one is Triple Modular Redundancy (TMR) and consists of having three entities calculating the same value and have a voter entity compare the results. The most common output value is assumed to be the correct one. This mechanism is explained in [8,10]. In the aforementioned mechanism more than twice the power is consumed, and a latency overhead is always required.

Fault-tolerant versions of SAR image generation algorithms are presented in [8,10,19]. [10] proposes a fault tolerance mechanism for the Fast-Fourier Transformer (FFT) algorithm based on range and azimuth compression by implementing Concurrent Error Detection (CED) and using weighted sum, and also implements scrubbing. [19] also presents a mechanism for FFT algorithm based on a weighted checksum encoding scheme. [8] describes a Fault-Management Unit which is responsible for the following functions: a scrub controller to periodically reload the FPGA configurations data, a fault detection circuit to periodically test the hardware, a switching circuit responsible for removing a faulty processor and replace it by an alternative processor, and a majority voter circuit, which is responsible for comparing the results of a TMR mechanism used during the SAR algorithm execution.

#### 2.5 Approximate Computing Fault Tolerance

If small variations in the computation of image processing algorithms are introduced, they may not be perceptible at all. Therefore, such algorithms allow some deviations from the correct value while still having valid images. In this context, this paper proposes a novel fault-tolerance mechanism which relies on approximations of the computations when in the presence of errors.

Reduced-Precision Redundancy (RPR) is used to reduce the overhead introduced by TMR by using a full-precision computation and two reduced-precision

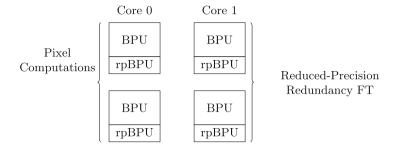

Fig. 2. Workload distribution of the developed fault tolerance mechanism between the CPU cores.

computations. RPR can be implemented in hardware, following an architecture similar to TMR, or software, following an architecture similar to temporal redundancy. The full-precision computation corresponds to the "original computation" and the other two computations to approximations. Computing the approximations reducing the overhead of the redundant computations, hence it is more efficient than calculating a full-precision values. However, the overhead of the voting process is kept constant. Examples of applications that use RPR are [12,17].

In [4], the authors proposed a mechanism for Single Event Upset (SEU) mitigation, which relies only on the comparison of the full-precision result against only one approximation, obtained from a Look-Up Table (LUT). Due to the lack of precision, only the Most Significant Bits (MSbs) are compared. It they are equal, the full-precision result is passed to the output of the arithmetic units, otherwise, the approximate result is used. While it is not possible to determine which unit is the acting as the faulty one, the full-precision computation is always more prone to error than the reduced one.

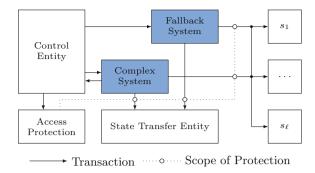

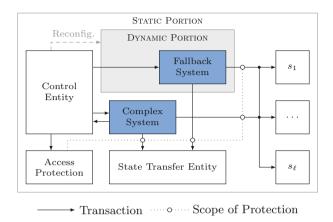

# 3 Dual-Core Fault-Tolerant SAR Imaging Architecture

#### 3.1 Proposed Architecture

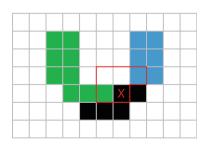

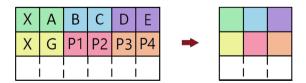

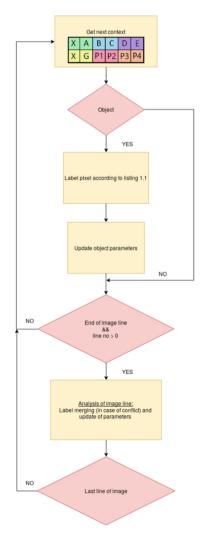

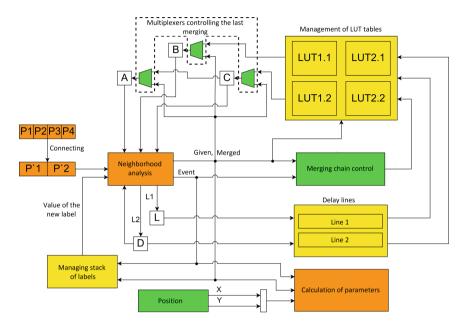

In the BackProjection algorithm, the pixel computations are the most intensive set of computations.

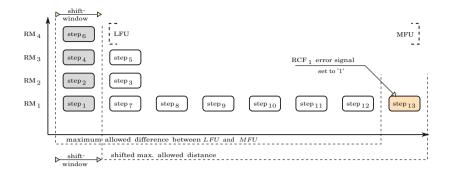

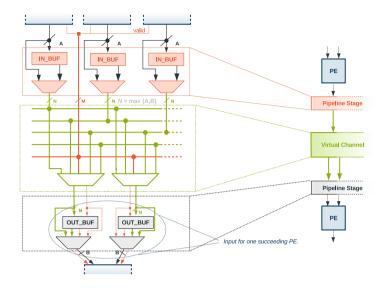

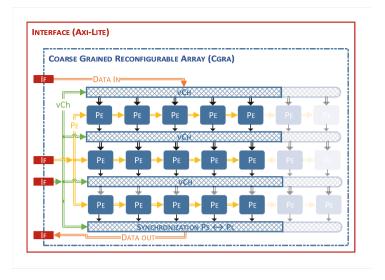

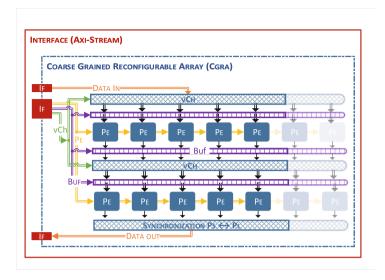

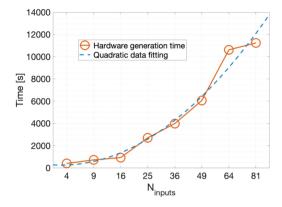

The calculation of each pixel, or Backprojection Unit (BPU), is done in parallel, which means each core computes one pixel at a time. For this reason, it is protected by RPR, reducing the total overhead in the system. A scheme of the architecture of the fault tolerance mechanism is displayed in Fig. 2, where it is possible to observe which parts of the Backprojection (BP) algorithm are protected. The approximations are calculated after the full-precision computations. The approximation computation and the error detection are represented in Fig. 2 as Reduced-Precision Backprojection Units (rpBPUs).

|        | Original | Pixels in batch   |                   |                   |                   |  |

|--------|----------|-------------------|-------------------|-------------------|-------------------|--|

|        |          | 4                 | 8                 | 16                | 32                |  |

| Core 0 | _        | $240.4\mathrm{s}$ | $240.6\mathrm{s}$ | $241.5\mathrm{s}$ | $241.7\mathrm{s}$ |  |

| Core 1 | _        | $239.9\mathrm{s}$ | $239.3\mathrm{s}$ | $241.0\mathrm{s}$ | $239.4\mathrm{s}$ |  |

| Total  | 477.4 s  | $480.3\mathrm{s}$ | $479.9\mathrm{s}$ | $482.6\mathrm{s}$ | $480.4\mathrm{s}$ |  |

**Table 2.** Dual-core execution times in function of the number of pixels per batch. The longer execution per batch number is displayed in bold in the table.

#### 3.2 Algorithm Parallelization

In this algorithm, the pixel computations have no dependencies, therefore, they can be computed in parallel. The workload was divided between the cores statically since dynamic load-balancing introduces overhead in the system. The results of this test are presented in Table 2, where the execution time is presented in function of the number of pixels per batch. The tested number of pixels per batch was 4, 8, 16 and 32.

From Table 2 it is possible to conclude that the number of BPUs per batch does not have a significant influence on the total execution time since it is smaller or equal than 1%. It is also possible to observe that the workload is relatively balanced, since there are not any accentuated differences in the execution times of each core. This leads to conclude that dynamic load-balancing is not necessary and that the batch number is also indifferent. The final chosen number of units per batch was 4, since it resulted in a similar execution time on both cores.

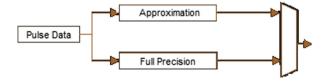

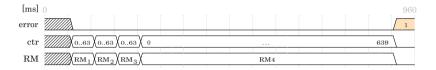

#### 3.3 Modified Reduced-Precision Redundancy

This work uses a modified version of the RPR mechanism, which computes only one approximation (rpBPU) after computing the full precision result (BPU) to perform the comparison. The architecture of the modified RPR mechanism is presented in Fig. 3.

Both full-precision and reduced-precision values are compared by computing their difference. If the difference is greater than an acceptable threshold (T) from the reduced-precision value, it is assumed the value is incorrect and the reduced-precision value is used instead. If not, the full-precision result is assumed correct and is used. The reduced-precision value is copied to the output when an error is detected because it is calculated in a shorter amount of time, and thus it is less likely to have been affected by a fault. The reduced-precision values are calculated using the aforementioned optimizations.

#### 3.4 Algorithm Profiling

To produce a reduced computation of the BPU it was necessary to profile the source code to determine which were the most time consuming operations. Moreover, the operations that last longer are the ones that are more prone to be subjected to error. In future work, this profiling will also be important to determine which operations to port into a hardware accelerator.

For profiling, the software implementation of the BackProjection algorithm ran on the target device, Zynq FPGA from Xilinx, with the small image as input. It took approximately 8 min to generate this image, using the o3<sup>1</sup> optimization level. Other image sizes required processing times greater than 156 min. The implementation of the algorithm was profiled using **gprof**<sup>2</sup>. Table 3 shows the percentage of time dedicated to the most time consuming instructions in the BackProjection algorithm.

| Operation | Execution time (%) |  |  |  |

|-----------|--------------------|--|--|--|

| Sine      | 42.05              |  |  |  |

| Cosine    | 42.54              |  |  |  |

| Others    | 15.41              |  |  |  |

Table 3. BackProjection algorithm profiling.

The trigonometric functions are responsible for over 80% of the execution time of the algorithm, which means that the potential for the reduced-precision redundancy mechanism lies within these functions. The rest of the algorithm, including input and output operations, is executed in under 16% of the time.

#### 3.5 Trigonometric Functions Optimization

The optimizations for the trigonometric functions tested are described below and the results are presented in Table 4.

- COordinate Rotation Digital Computer (CORDIC) algorithm [18];

- Taylor Series:

- Wilhem's LUT<sup>3</sup>;

Fig. 3. The architecture of the modified RPR fault-tolerance mechanism.

<sup>&</sup>lt;sup>1</sup> https://gcc.gnu.org/onlinedocs/gcc/Optimize-Options.html.

<sup>&</sup>lt;sup>2</sup> https://ftp.gnu.org/old-gnu/Manuals/gprof-2.9.1/html\_mono/gprof.html.

<sup>&</sup>lt;sup>3</sup> https://www.atwillys.de/content/cc/sine-lookup-for-embedded-in-c/.

| Design                 | Variation      | Time [s] | SNR [dB] |

|------------------------|----------------|----------|----------|

| Baseline               |                | 477.4    | 138.9    |

| CORDIC                 | 10 iterations  | 238.8    | 60.5     |

|                        | 15 iterations  | 262.7    | 90.5     |

|                        | 20 iterations  | 286.3    | 120.2    |

|                        | 25 iterations  | 311.3    | 136.1    |

|                        | 30 iterations  | 335.1    | 136.3    |

| Taylor Series          | 4 terms        | 186.0    | 71.8     |

|                        | 5 terms        | 192.3    | 103.8    |

|                        | 6 terms        | 201.5    | 133.6    |

|                        | 7 terms        | 210.4    | 135.3    |

| Wilhem's Look-Up Table | n/a            | 123.2    | 69.1     |

| Libfixmath             | Taylor I       | 179.3    | 54.5     |

|                        | Taylor II      | 158.8    | 33.6     |

|                        | LUT            | 134.8    | 99.2     |

| Ganssle                | 3 coefficients | 163.5    | 66.3     |

|                        | 4 coefficients | 167.3    | 105.2    |

|                        | 5 coefficients | 170.7    | 118.3    |

|                        | 7 coefficients | 176.5    | 134.8    |

|                        | 7 coefficients | 179.8    | 135.3    |

**Table 4.** Comparison of the results produced by different optimization algorithms for the trigonometric functions.

Observing the results on Table 4, the following conclusions can be drawn. All optimizations are indeed faster than the original version, which was expected. However, most of these optimizations lead to a large precision loss.

The implementation of the CORDIC algorithm used to test was developed by John Burkardt<sup>5</sup>. CORDIC is the algorithm with the worst performance, with all its tested versions being slower than any other version of another algorithm.

The results obtained from the Taylor Series algorithm were outperformed by the Ganssle methods, both in SNR and execution time.

The Wilhem's Look-Up Table method was the fastest overall and outperformed some variations of the other algorithms. It is a good alternative in systems with very limited memory since the LUT table occupies 66 bytes only, however, if memory does not represent an issue, the libfixmath library is a better alternative.

libfixmath<sup>4</sup>;

<sup>-</sup> Ganssle optimizations [9].

<sup>&</sup>lt;sup>4</sup> https://github.com/PetteriAimonen/libfixmath.

<sup>&</sup>lt;sup>5</sup> https://people.sc.fsu.edu/~jburkardt/c\_src/cordic/cordic.html.

Besides the LUT variation, libfixmath provides two functions based on Taylor Series. These two variations are outperformed by the Ganssle optimizations and even the author's Taylor Series implementation, with worse performance and less precision. libfixmath LUT variation is one of the best options for the BackProjection optimization.

The Ganssle optimizations are a good alternative to replace the trigonometric functions in the BackProjection algorithm. The first variation, the one that uses 3 coefficients to calculate the final result, is outperformed by both the LUT methods. Nevertheless, the other variations provide higher precision without a significant increase in the execution time. There are two functions that vary only in the type of variables they use: single precision or double precision. Double precision is more subject to errors since it requires more bitwise calculations and the gain in precision is not significant to the point of being worth computing them in prone to error environments. The 4-coefficient variation does not provide much more precision when compared to the libfixmath LUT function and the execution time increases by more than 30 s, making the former a better alternative. The 5-coefficient variation provides more precision with an execution time increase of less than 36 s. The 7-coefficient (implemented with single precision) function provides a precision very similar to the original, with a difference of only less than 4 dB in the SNR, and an increase of less than 43 s.

To sum up, the functions that represent a better option for the BackProjection algorithm optimization are the libfixmath LUT and the Ganssle variations of 5 and 7 coefficients. These three functions are used in the implementation of the RPR mechanism.

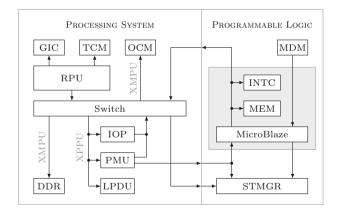

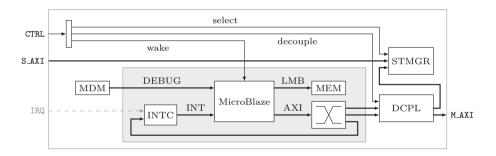

# 4 Implementation Results

The research design was implemented on a Pynq-Z2 board from TUL. This board contains a Zynq XC7Z020 device from Xilinx, an external 512MB DDR3 memory, and I/O peripherals. The Zynq device contains a Programmable Logic (PL) and a Processing System (PS). The PL corresponds to a Xilinx 7-series FPGA. The PS main components are a dual-core ARM Cortex-A9 processor and a memory controller.

#### 4.1 Precision Optimization Evaluation

Algorithm 1.1 was implemented using three precision reduction optimizations: the libfixmath LUT and the 5 and 7-coefficient Ganssle trigonometric functions. The execution times of the complete architecture for each of these optimizations is presented in Table 5. As can be observed, the architecture implemented using the libfixmath is 1.58 times faster than the serial original version of the algorithm. Regarding the 5-coefficient Ganssle algorithm, the execution was 1.50 times faster than the original and the 7-coefficient Ganssle algorithm was 1.49 times faster than the original version. When compared to the dual-core version of the BackProjection algorithm, the final architecture using the

| Design         | Baseline (single core) | Baseline (dual core) | Libfixmath | Ganssle<br>5-coef. | Ganssle<br>7-coef. |

|----------------|------------------------|----------------------|------------|--------------------|--------------------|

| Exec. time [s] | 477.4                  | 240.4                | 301.5      | 317.3              | 319.7              |

**Table 5.** Comparison between the execution times depending on the optimization.

5-coefficient Ganssle 7-coefficient Ganssle Optimization | libfixmath 55.4 37.9 -62.3#2 63.4 79.8 103.3

94.7

Table 6. Results of RPR with Agressive Fault-Injection.

libfixmath LUT method, the 5-coefficient and 7-coefficient Ganssle algorithms introduce an overhead of 25%, 32% and 33%, respectively.

82.1

#### 4.2 Solution Evaluation

$-\inf$

#1

#3

To test the developed architecture, a set of tests were performed. The fault injection was implemented in software and at compile-time by introducing bitflips according to a specific distribution. Measurements performed in the L2 space were reported in<sup>6</sup> and on average there is one SEU per day. However, other locations in space induce more bit-flips.

Regarding the Reduced-Precision Redundancy mechanism, the objective was to observe the final quality of the generated images, using the SNR, in the presence of faults. To test the this mechanism, the following tests were implemented. To inject faults, a fault injection function was called after every statement and a bit-flip could or not affect the last modified variable. The frequency of the bit-flips depends on the test.

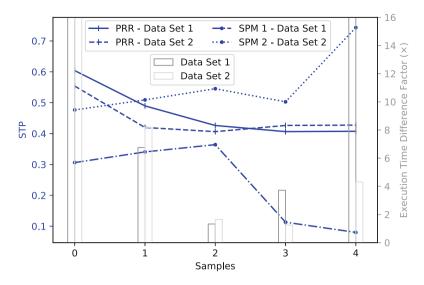

- Test RPR With Aggressive Fault Injection. The average occurrences of bit-flips in space is 1 per day. To evaluate the mechanism on a more aggressive scenario, with worse conditions, this fault injection follows a normal distribution with a mean value of 40 and a standard deviation of 5. The results of this test are presented in Table 6.

- Test RPR With 1440, 2880 and 8640 Bit-Flips per Day. Considering the average of bit-flips, a worse-case scenario was tested: an average of 1440 bit-flips per day, or one every 60, 30 and 10 s, respectively. The bit-flip affects a random bit in a random variable. The results of this test are presented in Table 7.

Each of the RPR tests was executed three times for each of the optimizations implemented: libfixmath, 5-coefficient and 7-coefficient Ganssle algorithms.

<sup>&</sup>lt;sup>6</sup> http://herschel.esac.esa.int/Docs/Herschel/html/ch04s02.html.

|      | Optimization |                       |                       |                    |  |

|------|--------------|-----------------------|-----------------------|--------------------|--|

|      | libfixmath   | 5-coefficient Ganssle | 7-coefficient Ganssle |                    |  |

| 1440 | #1           | 138.9 dB              | 138.8 dB              | $19.9\mathrm{dB}$  |  |

|      | #2           | 138.6 dB              | 138.5 dB              | $134.8\mathrm{dB}$ |  |

|      | #3           | 138.8 dB              | 138.8 dB              | $138.8\mathrm{dB}$ |  |

| 2880 | #1           | 97.8 dB               | $67.9\mathrm{dB}$     | $109.9\mathrm{dB}$ |  |

|      | #2           | 8.3 dB                | 129.1 dB              | $34.4\mathrm{dB}$  |  |

|      | #3           | $90.3\mathrm{dB}$     | 101.1 dB              | $83.3\mathrm{dB}$  |  |

Table 7. Results of RPR with 1440, 2880, and 8640 bit-flips per day.

#### 5 Discussion

The overall results for the executions with injection of 1440 bit-flips were close to the original SNR value of the image, except the first execution of the 7-coefficient Ganssle algorithm. The other iterations deviated from the original value a maximum of 4.1 dB and an average of 0.65 dB, when in the presence of errors. The low SNR value of the first iteration of the 7-coefficient Ganssle algorithm is justified by the fault injection in random variables. Certain variables are more critical than others, for example, the final result of the approximation has a greater impact on the final image quality.

Most of the results for very aggressive error rates were not considered acceptable, since the SNR values are inferior to 100 dB. Two iterations, the third of libfixmath and the first of the 7-coefficient Ganssle algorithm were either minus infinite or a negative value, which generate a blank image.

The overall SNR values obtained for 2880 bit-flips are inferior when compared to the results of 1440 bit-flips, which was expected since the rate of bit-flips doubled. The 5-coefficient Ganssle algorithm provided the best results of this test: two out of three SNR values are considered acceptable and the other has a SNR almost half of the original value. The results obtained using the 7-coefficient Ganssle algorithm generate one acceptable image. For this test, the optimization which provided the best results was the 5-coefficient Ganssle algorithm.

The rate of 8640 bit-flips represents a fault injection of 10 bit-flips per second. At this rate the proposed mechanism was not successful at detecting and correcting faults. The values in the results table are nan,  $-\infty$  or negative values, which generate a blank image. A SNR equal to nan happens when a bit-flip affects a floating-point variable and the resulting value is not considered a valid floating-point representation. Regarding the SNR of  $-\infty$ , the calculation of this metric involves a logarithm operation, which equals  $-\infty$  in C when calculating the logarithm of 0. The mechanism became ineffective due to the elevated rate of bit-flips, leading to the conclusion the mechanism is only able to tolerate a certain rate of faults.

#### 6 Conclusions and Future Work

This work explored the research and development of a fault-tolerant architecture for SAR imaging systems capable of generating SAR images using the Backprojection Algorithm in a space environment.

The modified RPR mechanism proposed avoids the use of more costly mechanisms, such as TMR, while taking advantage of the dual-core processor on the Zynq device to improve performance. The main drawback of this mechanism, is the inability to detect or correct control errors.

The final architecture consists of a dual-core implementation of the Backprojection Algorithm, protected by the modified Reduced-Precision Redundancy mechanism. Depending on the optimization used, the overhead of the fault tolerance mechanism ranges from 25% to 33% when compared to the dual-core version of the Backprojection Algorithm.

In spite of the limitations of a software implementation the modified RPR mechanism, the algorithm was tested under pessimistic conditions, different from the average use scenario. Furthermore, the developed architecture with an approach of RPR was demonstrated to be a good alternative for intensive space applications. Future work involves exploring optimization techniques such as the ones described in [5–7].

#### References

- Barker, K., et al.: PERFECT (Power Efficiency Revolution For Embedded Computing Technologies) Benchmark Suite Manual. Pacific Northwest National Laboratory and Georgia Tech Research Institute, December 2013. http://hpc.pnnl.gov/projects/PERFECT/

- Baumann, R.C.: Radiation-induced soft errors in advanced semiconductor technologies. IEEE Trans. Device Mater. Reliab. 5(3), 305–316 (2005). https://doi.org/10.1109/TDMR.2005.853449

- Claeys, C., Simoen, E.: Radiation Effects in Advanced Semiconductor Materials and Devices. Springer, Heidelberg (2002). https://doi.org/10.1007/978-3-662-04974-7

- Duarte, R.P., Bouganis, C.: Zero-latency datapath error correction framework for over-clocking DSP applications on FPGAs. In: 2014 International Conference on ReConFigurable Computing and FPGAs (ReConFig14), pp. 1–7, December 2014. https://doi.org/10.1109/ReConFig.2014.7032566

- Duarte, R.P., Bouganis, C.S.: High-level linear projection circuit design optimization framework for FPGAs under over-clocking. In: 2012 22nd International Conference on Field Programmable Logic and Applications (FPL), pp. 723–726. IEEE (2012)

- Duarte, R.P., Bouganis, C.-S.: A unified framework for over-clocking linear projections on FPGAs under PVT variation. In: Goehringer, D., Santambrogio, M.D., Cardoso, J.M.P., Bertels, K. (eds.) ARC 2014. LNCS, vol. 8405, pp. 49–60. Springer, Cham (2014). https://doi.org/10.1007/978-3-319-05960-0\_5

- Duarte, R.P., Bouganis, C.S.: ARC 2014 over-clocking KLT designs on FPGAs under process, voltage, and temperature variation. ACM Trans. Reconfigurable Technol. Syst. 9(1), 7:1–7:17 (2015). https://doi.org/10.1145/2818380

- 8. Fang, W.C., Le, C., Taft, S.: On-board fault-tolerant SAR processor for space-borne imaging radar systems. In: 2005 IEEE International Symposium on Circuits and Systems, vol. 1, pp. 420–423, May 2005. https://doi.org/10.1109/ISCAS.2005. 1464614

- 9. Ganssle, J.: The Firmware Handbook. Academic Press Inc., Orlando (2004)

- Jacobs, A., Cieslewski, G., Reardon, C., George, A.: Multiparadigm computing for space-based synthetic aperture radar (2008)

- 11. Maki, A.: Space radiation effect on satellites. Joho Tsushin Kenkyu Kiko Kiho **55**(1–4), 43–48 (2009)

- Pratt, B., Fuller, M., Wirthlin, M.: Reduced-precision redundancy on FPGAs (2011). https://doi.org/10.1155/2011/897189

- Pritsker, D.: Efficient global back-projection on an FPGA. In: 2015 IEEE Radar Conference (RadarCon), pp. 0204–0209, May 2015. https://doi.org/10. 1109/RADAR.2015.7130996

- 14. Sinclair, D., Dyer, J.: Radiation effects and cots parts in smallsats (2013)

- Sørensen, J., Santin, G.: The radiation environment and effects for future ESA cosmic vision missions. In: 2009 European Conference on Radiation and Its Effects on Components and Systems, pp. 356–363, September 2009. https://doi.org/10.1109/RADECS.2009.5994676

- Tambara, L.A.: Analyzing the impact of radiation-induced failures in all programmable system-on-chip devices (2017)

- Ullah, A., Reviriego, P., Pontarelli, S., Maestro, J.A.: Majority voting-based reduced precision redundancy adders. IEEE Trans. Device Mater. Reliab. PP(99), 1 (2017). https://doi.org/10.1109/TDMR.2017.2781186

- 18. Volder, J.: The cordic computing technique. In: Papers Presented at the 3–5 March 1959, Western Joint Computer Conference, IRE-AIEE-ACM 1959 (Western), pp. 257–261. ACM, New York (1959). https://doi.org/10.1145/1457838.1457886

- Wang, S.J., Jha, N.K.: Algorithm-based fault tolerance for FFT networks. IEEE Trans. Comput. 43(7), 849–854 (1994). https://doi.org/10.1109/12.293265

- Ya'acob, N., Zainudin, A., Magdugal, R., Naim, N.F.: Mitigation of space radiation effects on satellites at low earth orbit (LEO). In: 2016 6th IEEE International Conference on Control System, Computing and Engineering (ICCSCE), pp. 56– 61, November 2016. https://doi.org/10.1109/ICCSCE.2016.7893545

# Optimizing CNN-Based Hyperspectral Image Classification on FPGAs

Shuanglong Liu<sup>1(⊠)</sup>, Ringo S. W. Chu<sup>2</sup>, Xiwei Wang<sup>3</sup>, and Wayne Luk<sup>1</sup>

- Department of Computing, Imperial College London, London, UK

{s.liu13,w.luk}@imperial.ac.uk

- <sup>2</sup> Department of Computer Science, University College London, London, UK ringo.chu.16@ucl.ac.uk

- <sup>3</sup> China Academy of Space Technology, Beijing, China wangxiwei@gmail.com

Abstract. Hyperspectral image (HSI) classification has been widely adopted in remote sensing imagery analysis applications which require high classification accuracy and real-time processing speed. Convolutional neural networks (CNNs)-based methods have been proven to achieve state-of-the-art accuracy in classifying HSIs. However, CNN models are often too computationally intensive to achieve real-time response due to the high dimensional nature of HSI, compared to traditional methods such as Support Vector Machines (SVMs). Besides, previous CNN models used in HSI are not specially designed for efficient implementation on embedded devices such as FPGAs. This paper proposes a novel CNN-based algorithm for HSI classification which takes into account hardware efficiency and thus is more hardware friendly compared to prior CNN models. An optimized and customized architecture which maps the proposed algorithm on FPGA is then proposed to support real-time on-board classification with low power consumption. Implementation results show that our proposed accelerator on a Xilinx Zynq 706 FPGA board achieves more than 70× faster than an Intel 8-core Xeon CPU and  $3\times$  faster than an NVIDIA GeForce 1080 GPU. Compared to previous SVM-based FPGA accelerators, we achieve comparable processing speed but provide a much higher classification accuracy.

Keywords: Hyperspectral image classification  $\cdot$  Deep learning  $\cdot$  Convolution neural network  $\cdot$  Field-programmable gate array

#### 1 Introduction

Hyperspectral images (HSI) contain spectrum information for each pixel in the image of a scene, and can be used in finding objects and identifying materials or detecting processes [4]. Hyperspectral images are widely employed in many

The first two authors contributed equally.

<sup>©</sup> Springer Nature Switzerland AG 2019

C. Hochberger et al. (Eds.): ARC 2019, LNCS 11444, pp. 17-31, 2019.

applications from airborne and satellite remote sensing mission [19], to oil spill detection [16], early cancer diagnosis [15] and environmental monitoring [14]. HSI classification involves assigning a categorical class label to each pixel in the image, according to the corresponding spectral and/or spatial feature [2]. With the advent of new hyperspectral remote sensing instruments and their increased temporal resolutions, the availability and dimensionality of hyperspectral data are continuously increasing [12]. This demands very fast processing solutions for on-board space platforms in order to reduce download bandwidth and storage requirements [19], making reconfigurable hardware such as FPGAs very promising to perform and accelerate HSI classification methods.

Among the approaches explored for HSI classification, convolutional neural network (CNN) based methods such as BASS Net [17] and HSI-CNN [13] are favourable over the others because of their greatly improved accuracy for some popular benchmark datasets, with the ability to use extensive parameters to learn spectral features of a HSI. However, these CNN-based algorithms have great computational complexity due to the large dimensionality of hyperspectral images. Besides, prior CNN models used in HSI classification may not be hardware efficient to be deployed on embedded systems such as FPGAs without any modifications since they are not specially designed for FPGAs.

In order to address the above challenges and achieve fast processing speed on embedded devices, this work proposes a novel CNN architecture based on BASS Net [17], and our model is more hardware efficient for implementation on FPGAs while maintaining similar accuracy as the original BASS Net. Besides, we propose and optimize the hardware architecture to accelerate our proposed network in FPGA by parallel processing, data pre-fetching and design space exploration. Compared to previous SVM-based FPGA accelerators, the proposed accelerator has almost the same scale of processing speed on the same scale of FPGA device, but provides a lot higher accuracy results.

The main contributions of this work are summarized as follows:

- A novel network for HSI classification which takes into account hardware efficiency, and thus achieves real-time on-board HSI classification with both high accuracy and fast processing speed (Sect. 3);

- A highly optimized hardware architecture which maps the proposed CNN model onto FPGAs, and it processes all the layers in on-chip memories to enable high throughput of real-time HSI applications (Sect. 4);

- Evaluation of the proposed accelerators on a Xilinx ZC706 FPGA board across four popular benchmark datasets. Our accelerator achieves an overall classification accuracy of 95.8%, 99.4%, 95.2% and 98.2% respectively which largely outperforms previous SVM-based FPGA accelerators, and it achieves around 10 to 25 us/pixel processing speed which is about 80× and 3× faster than the respective CPU and GPU designs (Sect. 5).

### 2 Background and Related Work

#### 2.1 Hyperspectral Imagery

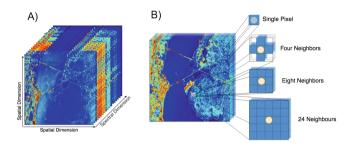

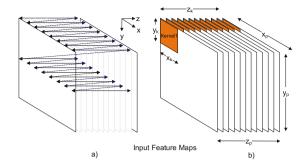

Unlike traditional RGB image, hyperspectral images are typically represented as a data cube in dimension  $(x, y, \lambda)$ , where x and y represent spatial dimensions with space information of pixels, and  $\lambda$  represents the third dimension with spectral information for distinguishing different materials and objects.

Hyperspectral image (HSI) classification is the task to assign a class label to every pixel in an image. Several approaches have been explored in literature for HSI classification. K-nearest neighbors (k-NN) based methods use Eucledian distance in the input space to find the k nearest training examples and a class is assigned on the basis of them [17]. Support Vector Machine (SVM) based methods introduce dimensionality reduction in order to address the problem of high spectral dimensionality and scarcity of labeled training examples, with SVM classifiers used in the reduced dimensional space. Although these methods adopt parallel processing [19] and are suitable for FPGA-based acceleration, they often behave weakly in terms of the classification accuracy when tackling large datasets [17].

#### 2.2 CNN-Based HSI Classification

Recently, deep learning based methods have achieved promising performance in HSI classifications [3] due to their ability to use extensive parameters to learn features. Deep learning methods [20] utilize spectral-spatial context modeling in order to address the problem of spatial variability of spectral signatures. These methods often use convolutional neural networks (CNNs) for feature learning and classification in an end-to-end fashion. CNNs adopt extensive parameter-sharing to tackle the curse of dimensionality. They extract and learn representative features via multiple times of back propagation. Using features is more effective than rule-based algorithms for recognition tasks.

One of the most popular CNN models for HSI classification is BASS Net [17]: a deep neural network architecture that learns band-specific spectral-spatial features and gives state-of-the-art performance without any kind of data-set augmentation or input pre-processing. While this algorithm leads to high classification performance due to efficient band-specific feature learning, the model is very computationally intensive, which often requires huge amount of resources and energy. Nevertheless, this network has parallelism in many computational blocks and thus can be prallelized in hardware platforms such as FPGAs. However, the BASS Net is not suitable to be deployed on embedded systems without modification. The main challenge is that the CNN architecture does not have identical layer parameters, which increases the difficulty of designing generic hardware modules that support varying parameters. For example, there are 1-D convolutional layers with different kernel sizes such as  $3 \times 1$  and  $5 \times 1$  implemented using spectral information and 2-D convolutional layers applied using spatial information. Fully-connected layers are also applied after all convolution

layers for summarization and output classification probability. Because of these reasons, direct mapping of this algorithm to FPGAs may not be efficient and cannot satisfy the requirement of real-time processing without the proposal of algorithm adaptions and efficient hardware architecture.

#### 2.3 Related Work

Prior work includes deploying SVM-based HSI classification on FPGA for acceleration and utilizing GPUs for algorithmic speed up on CNN-based methods. There is exhaustive literature on accelerating the traditional algorithms such as SVMs using FPGAs. Wang et al. [19] proposed a novel accelerator architecture for real-time SVM classification. The accelerator uses data flow programming to achieve high performance and can be usd for different applications. Tajiri et al. [18] proposed a hyperspectral image classification system on FPGA, by introducing the Composite Kernel Support Vector Machine and reducing the computational complexity. These former accelerators achieve real time processing speed but they do not achieve high classification accuracy and therefore are not favoured over CNN-based methods.

Recently CNN-based HSI approaches have been proposed by many researchers. Santara et al. [17] presented an end-to-end deep learning architecture that extracts band specific spectral-spatial features and performs landcover classification. Luo et al. [13] proposed a novel HSI classification model to reorganize data by using the correlation between convolution results and to splice the onedimensional data into image-like two-dimensional data to deepen the network structure and enable the network to extract and distinguish the features better. Lee et al. [5] built a fully convolutional neural network with a total of 9 layers, which is much deeper than other convolutional networks for HSI classification. To enhance the learning efficiency of the proposed network trained on relatively sparse training samples, residual learning was used in their work. However, all of these efforts have only focused on the improvement of the accuracy of these algorithms on CPU or GPUs, the performance of their models have never been reported or considered in prior works. Therefore, it is unclear if these algorithms are suitable for on-board platforms and it is not straightforward to map them into embedded devices for real-time processing.

To the best of the authors' knowledge, this is the first work that proposes FPGA architecture for CNN-based HSI classifications. Our FPGA-based accelerator achieves high accuracy, fast processing speed and lower power consumption, which is suitable for on-board space platforms.

# 3 Proposed CNN-Based HSI Classification Model

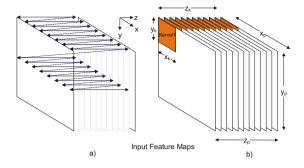

Deep neural network architectures such as BASS Net are based on pixel-wise classification results of the input image. That is to say, for each pixel, the input to the network is the pixel  $X_i$  from the image with its  $p \times p$  neighbourhoods (for spatial context) in the form of a  $p \times p \times N_c$  volume, where  $N_c$  is the spectral

bands of the dataset scene, i.e., the number of channels of the input image, and p is called the patch size. The output of the network is the predicted class label  $y_i$  for  $X_i$ . Leng et al. [6] studied different strategies to take account of neighbour pixels and extract smaller spectral cube with labelled central pixel from a HSI for training samples. These strategies are single pixel, four neighbour pixels and eight neighbour pixels, i.e., the patch size is 3, as shown in Fig. 1.

Fig. 1. (A) Hyperspectral Image cube. (B) Extraction of data cube with labeled at central pixel from a raw HSI.

#### 3.1 Structure Description

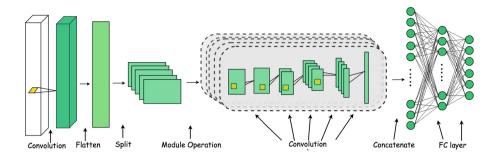

We propose our network based on the structure of BASS-Net [17]. The motivation behind the network is that it uses significantly fewer parameters compared to other models and exhibits parallelism at inference stage. We further modify the model such that it is more efficient for FPGA implementation. The patch strategy is altered to 24 neighbours, i.e., the input patch size is 5 (see Fig. 1) to adapt our model as it performs even better on HSI classification procedures. The proposed model processes through the following three stages at both training and inference, as shown in Fig. 2.

Spectral Feature Selection and Band Partitioning. In this step, the  $p \times p \times N_c$  input volume is taken as input by a  $3 \times 3$  or  $1 \times 1$  spatial convolution for feature selection; then the spectral dimension of the output is split into  $N_b$  bands with equal bandwidth and passed as input to the second step for parallel processing;

Spectral Feature Learning. This step applies  $N_b$  parallel networks, with one for each band: the input is first flattened to one dimension along the spatial dimensions; a  $3 \times 3$  convolution filter is applied in the spectral dimension to learn spectral features; the outputs of the parallel networks are then concatenated and fed into the summarization and classification stage.

Summarization and Classification. This step summarizes the concatenated outputs of the band-specific networks of the previous stage by using a set of fully connected layers, each of which is followed by a ReLU layer. A C-way softmax layer performs the final classification by calculating the conditional probabilities of the C output classes.

Fig. 2. Overall structure of our model architecture.

#### 3.2 Hardware Adaptations

There are some tunable parameters in the network architecture for different design choices: the input patch size p, the number of parallel bands  $N_b$  in the second stage and the convolutional kernel in the first stage. Compared to BASS Net, three major changes are introduced for hardware efficiency and accuracy improvement:

- (1) We utilized  $3 \times 3$  CNN filters in stage 1 for spatial dimension learning, which amplifies spatial signatures and are identical to the convolutions in stage 2;

- (2) 1-D convolutions of kernel size  $3 \times 1$  and  $5 \times 1$  in stage 2 are all replaced by 2-D  $3 \times 3$  fixed kernel size for generic hardware module design and reuse, thus the accuracy is improved due to the increased parameters;

- (3) In stage 2, the data are flattened along the spatial dimension and split into  $N_b$  segments along the spectral dimension. We choose  $N_b$  from 2, 4 or 8 for easy parallel processing in FPGA technology.

For block 1, we also apply  $3 \times 3$  convolution for input patch size of  $5 \times 5 \times N_c$  or  $1 \times 1$  convolution for input patch size of  $3 \times 3 \times N_c$ . One of the strategies is chosen for different datasets in order to have a trade-off between the accuracy and processing speed.

Our final network<sup>1</sup> parameter configurations are summarized in Table 1, and the final choices of  $N_b$  for different datasets are described in Sect. 5.1.

#### 3.3 Training Process

Regularization Methods. Trainable parameters are shared across each band in block 2 in order to minimize hardware resources and design space. Bands must be placed sequentially to allow back-propagation and avoid gradient vanishing problem. Dropout is applied on the fully-connected layers in block 3 to prevent over-fitting.

https://github.com/custom-computing-ic/CNN-Based-Hyperspectral-Image-Classification.

| Input pa                                | atch size:  | $5 \times 5 \times 220$ and $N_b$ | = 4                        |                         |                                    |  |

|-----------------------------------------|-------------|-----------------------------------|----------------------------|-------------------------|------------------------------------|--|

| Layer                                   |             | Type                              | Input volume Output volume |                         | Kernel                             |  |

| Block 1                                 | layer 1     | $3 \times 3$ conv                 | $5 \times 5 \times 220$    | $3 \times 3 \times 220$ | $3 \times 3 \times 220 \times 220$ |  |

| Split int                               | o $N_b$ bar | nds along spectral din            | nension and eac            | ch is run in Blcok      | : 2                                |  |

| Block 2                                 | layer 1     | $3 \times 3$ conv                 | $9 \times 55 \times 1$     | $7 \times 53 \times 2$  | $3 \times 3 \times 1 \times 2$     |  |

|                                         | layer 2     | $3 \times 3$ conv                 | $7 \times 53 \times 2$     | $5 \times 51 \times 4$  | $3 \times 3 \times 2 \times 4$     |  |

|                                         | layer 3     | $3 \times 3$ conv                 | $5 \times 51 \times 4$     | $3 \times 49 \times 4$  | $3 \times 3 \times 4 \times 4$     |  |

|                                         | layer 4     | $3 \times 3$ conv                 | $3 \times 49 \times 4$     | $1 \times 47 \times 4$  | $3 \times 3 \times 4 \times 4$     |  |

| The output of $N_b$ Blocks concatenated |             |                                   |                            |                         |                                    |  |

| Block 3                                 | layer 1     | Fully Connect layer               | $752 \times 1$             | $120 \times 1$          | $752 \times 120$                   |  |

|                                         | layer 2     | Fully Connect layer               | $120 \times 1$             | $9 \times 1$            | $120 \times 9$                     |  |

**Table 1.** The proposed CNN-based HSI network with input patch size  $5 \times 5$  and  $N_b = 4$ .

Loss Functions. We employ cross-entropy loss function as error measure. The training process aims to minimise the loss value to obtain a distribution that is the best capture of the data set. Given a training dataset:  $\{X_i, y_i\}_{i=1}^N$ , the designated loss function is described as:

$$\mathcal{L}(p,\hat{p}) = -\sum_{i=1}^{N} p(x) \log \hat{p}(x)$$

(1)

where p(x) is the probability distribution of our models, and  $\hat{p}(x)$  is the actual distribution that represents the dataset.

Optimizer. We used Adaptive Moment Estimation to update kernel weights and biases with initial learning rate 0.0005,  $\beta_1 = 0.9$  and  $\beta_2 = 0.999$ .

# 4 Proposed CNN-Based HSI Accelerator

#### 4.1 Hardware Architecture

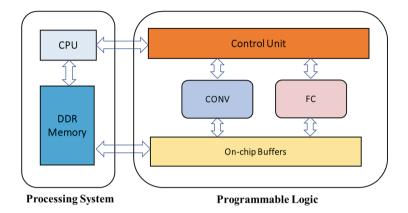

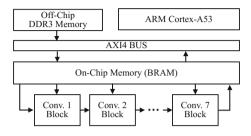

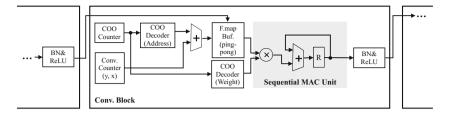

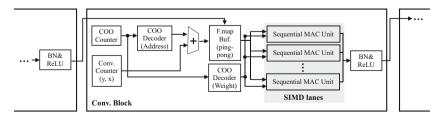

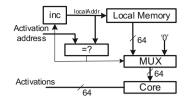

Based on our proposed network, we design the hardware architecture of the FPGA accelerator for CNN-based real-time HSI classification shown in Fig. 3. The proposed CNN accelerator design on FPGA is composed of several major components: the computation units (CONV and FC modules), on-chip buffers, external memory and control unit. The processor (PS) configures the parameters of the layers for the two computation units through the control unit. CONV and FC are the basic computation units for the CNN-based HSI classification algorithm. Due to the limitation of the on-chip memory size, the input data and weights of all the layers are stored in off-chip memories and transferred to on-chip buffers when processing each layer. All intermediate data for processing are stored in on-chip buffers to avoid frequent off-chip memory access. Therefore,

the required on-chip buffers need to store at least the input and output data size of one layer, since these on-chip buffers will be reused when the next layer is processed.

Fig. 3. The architecture of the FPGA-based CNN accelerator which integrates 2 computation units: CONV and FC.

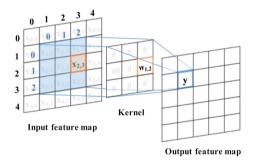

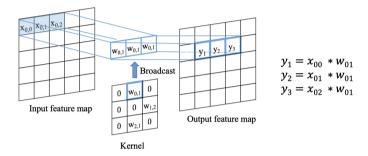

#### 4.2 Convolution and Fully-Connected Design

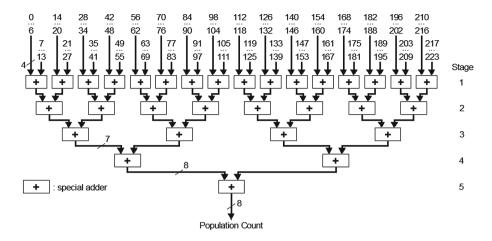

Our convolutional and fully-connected layer architectures are inspired by the design in [21]. The CONV unit contains several computational kernels running in parallel, and each kernel consists of 9 multipliers followed by an adder tree to implement the  $3 \times 3$  2-D convolution operation. Multiple kernels are utilised for parallel channel and filter processing and the total number of kernels represents the parallelism of the CONV unit  $(P_C)$ . Besides, we implement  $1 \times 1$  convolutions in the CONV kernel by reusing the 9 multipliers and bypassing the adder trees. Therefore, the degree of parallelism of  $1 \times 1$  CONV is 9 times of  $P_C$ .

The operation of the FC kernel is to perform dot product between the reshaped input feature vector and the weight matrix. The FC kernel also contains several multipliers to calculate the dot product between each row of the weight matrix and the feature vector in parallel. The number of multipliers in the FC kernel represents the parallelism of the FC unit  $(P_F)$ .

#### 4.3 Optimizations

In this section, we describe the optimization techniques used for the FPGA-based HSI accelerator design in order to increase the system throughput. The optimizations to the FPGA-based accelerator mainly focus on: (1) fully utilising the existing hardware resource to reduce the computation time by parallel processing [8], and (2) increasing the data reuse to reduce the communication time to off-chip memories [7].

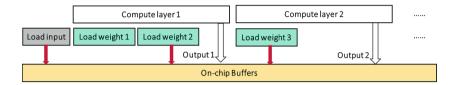

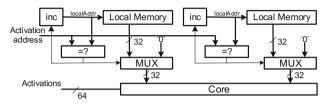

Data Pre-fetching and Pipelining. We adopt the parallel processing of multiple data and filters inside the CONV and FC kernel to increase the data reuse and reduce computation overhead. However, there is another overhead involving the transfer of the weights from DDR memory to the computational units. These weights actually do not need to be stored in on-chip buffers as they are only used once which is different from input data. To reduce this overhead, weights are pre-fetched before processing in order to overlap weight transfer time and computation. Figure 4 shows the timing of several computation and weight transfer phases.

Fig. 4. Computation and weights transfer flows.

To compute the first layer, we first load input data and weights of layer 1 and 2 from DDR memory to on-chip buffers. At the same time, the computation of layer 1 can start as soon as the weights of layer 1 are valid since the input data are already in on-chip buffers; after the computation of layer 1, the output of layer 1 has already been stored in the on-chip buffers and the weights of layer 2 have loaded to the memories, so we can process layer 2 immediately after finishing layer 1 and at the same time we load the weights for the next stage, i.e., layer 3. As a result, the total execution time only needs to cover the transfer of the input and the final output, and the computational time. All the weight transfer time is overlapped in the computation stage, and there is no waiting time between computations of two consecutive layers.

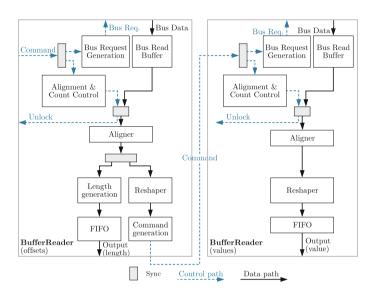

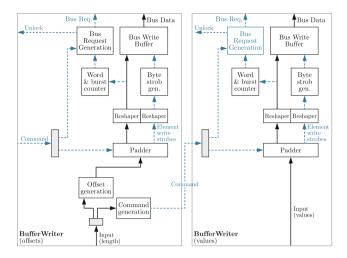

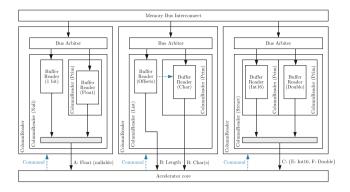

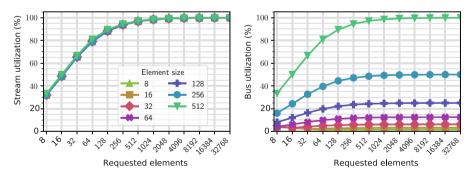

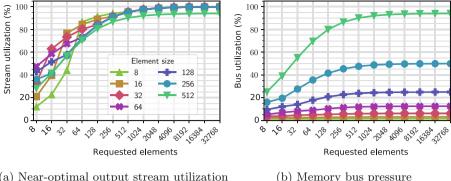

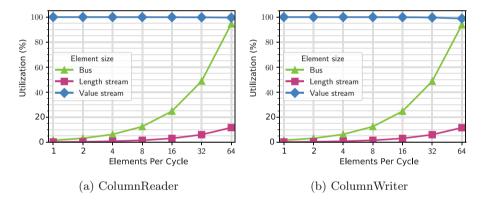

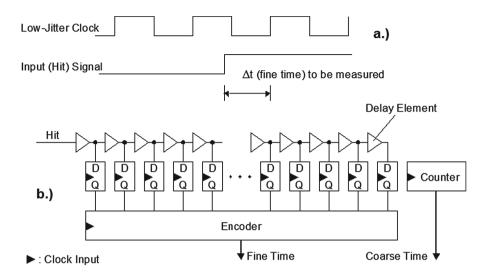

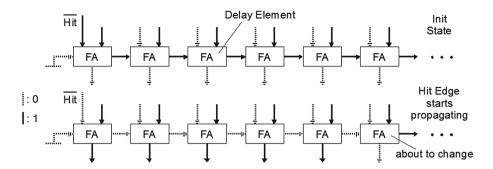

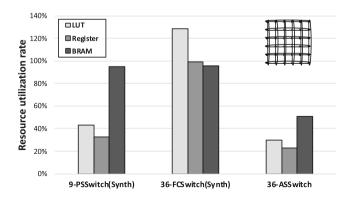

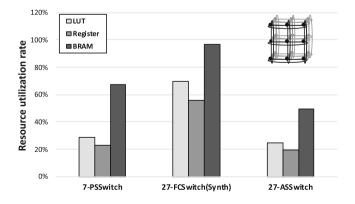

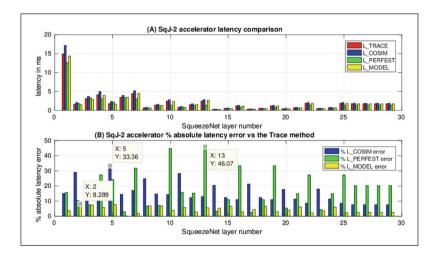

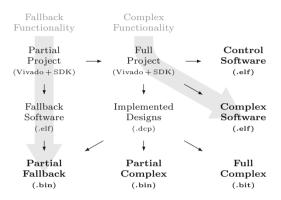

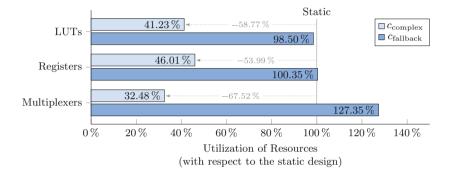

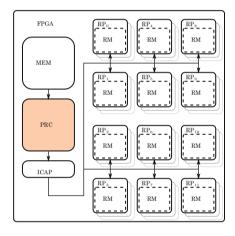

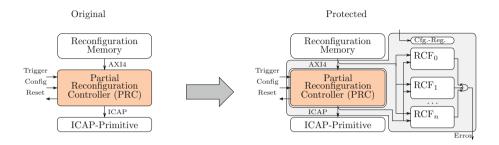

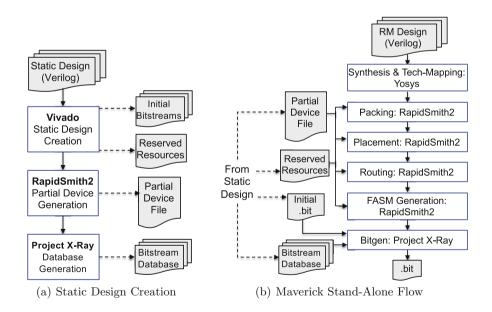

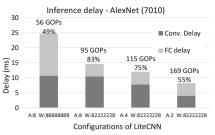

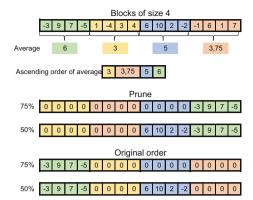

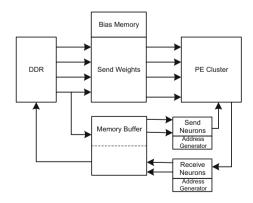

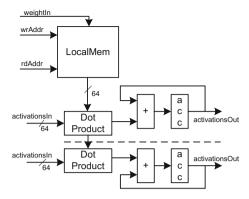

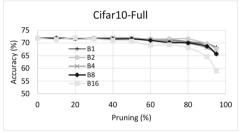

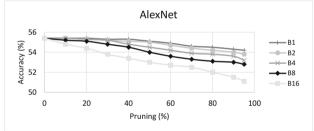

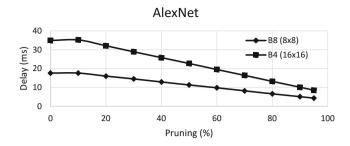

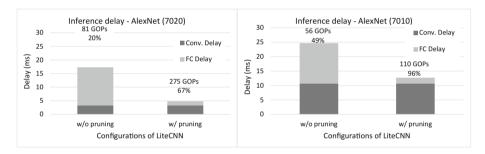

Data Quantization. The main benefit of accelerating CNN models in FPGAs comes from the fact that CNNs are robust to low bitwidth quantization [11]. Instead of using the default double or single floating point precision in CPU, fixed-point precision can be used in FPGA-based CNN accelerator to achieve an efficient design optimized for performance and power efficiency [9,10]. In this work, we implement our proposed design with 16 bit fixed-point which has been shown to achieve almost the same accuracy as floating point in the inference stage, in order to allow optimizations for high parallelism mentioned in the above section. It should be noted that there is no significant accuracy loss in the HSI classification result when reducing the precision from 32-bit floating point to 16-bit fixed-point quantized version for the inference process, as long as the training stage adopts 32-bit floating point.